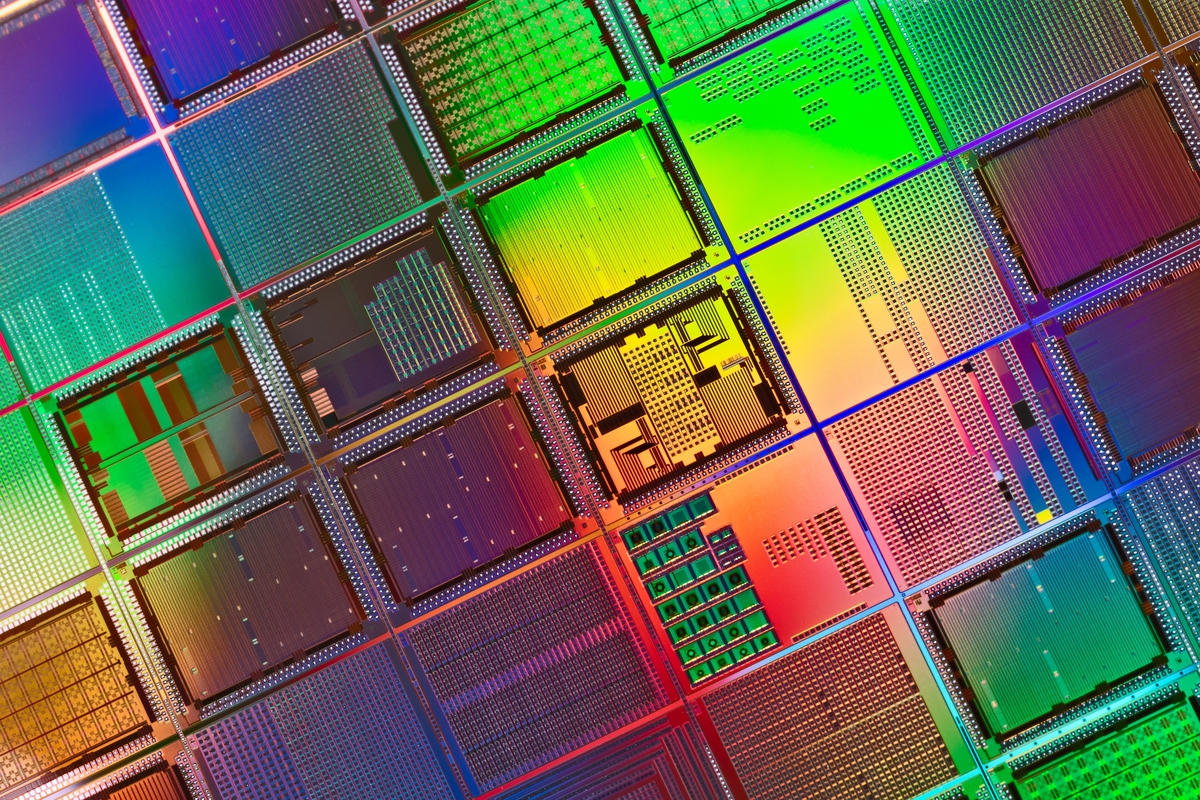

MSU Leveraging Intel 16 and the Cadence Tool Flow for Academic Chip Tapeout

Morgan State University (MSU) recently received an Apple Innovation Grant, designed to support engineering schools as they develop their silicon and hardware technologies. The New Silicon Initiative (NSI) is designed to inspire and prepare students for careers in hardware engineering, computer architecture, and silicon chip design.

Innovative professors, such as MSU's Dr. Kevin Kornegay and others responsible for delivering on the NSI goals, are leveraging the funding and support to create invaluable, hands-on experiences for their students. MSU faculty can enhance the NSI curriculum by inviting subject matter experts to provide guest lectures on topics such as integrated circuit design and computer architecture, providing practical insight regarding the theory and practice of silicon design. The course sequence starts with "Introduction to Electrical and Computer Engineering" (EEGR 105), where sophomores learn hands-on skills in circuit design, and works up to the critical class in the NSI program: the new "Tapeout Course in Digital Integrated Circuit Design" (EEGR 463). EEGR 463 ran in parallel with a similar course offered at UC Berkeley, where the lectures, assignments, and labs were the same, and the UC Berkeley instructors were in lock step with the teaching assistants at MSU.